## FUJITSU MICROELECTRONICS

## MB8876A MB8877A

October 1986

# FLOPPY DISK FORMATTER/CONTROLLER (FDC)

#### DESCRIPTION

The Fujitsu MB8876A and MB8877A are one-chip Floppy Disk Formatter/Controllers (FDC) which are fabricated with N-channel E/D MOS technology. They can be applied to any single density floppy disk, double density floppy disk and mini floppy disk.

The IBM3740 format and the frequency modulation (FM) recording are used for the single density

storage, and the IBM System-34 format and the modified frequency modulation (MFM) recording are used for the double density storage.

The MB8867A and MB8877A interface with an 8-bit parallel microprocessor to control data transfer and mechanical operation. They are packaged in a standard 40-pin dual in-line package.

# in dilliguidung

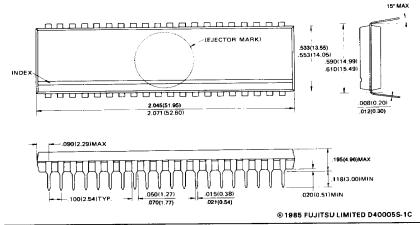

CERAMIC DIP DIP-40C-A01

PLASTIC DIP

#### **FEATURES**

Interface to 8-bit Microprocessor MB8876A: Negative-logic 8-bit Data Bus

MB8877A: Positive-logic 8-bit Data Bus

- IBM Compatible Sector Format

- Automatic Track Seeking and Verification

- Both Single and Double Density Formats

- a) Single Density in IBM3740 Format and FM Recording

- b) Double Density in IBM System-34 Format and MFM Recording

- Programmable Single Sector/ Multiple Sectors/Entire Track Read Operation

- Programmable Single Sector/ Multiple Sectors/Entire Track Write Operation

- Programmable Side Compare Function

- Programmable Sector Length

- Programmable Head Step Rate

- Applicable to Single Density, Double Density, and Mini Floppy Disks

- Programmable Head Engage/Head Settle Time

- Double Buffered Data I/O

- DMA Data Transfer Capability

- Write Precompensation Capability

- All TTL Compatible I/O

- Single + 5V Power Supply

- N-Channel Silicon-gate E/D MOS Process

- MB8876A: Upward Compatible with Western Digital FD1791-02

- MB8877A: Upward Compatible with Western Digital FD1793-02

- Two Package Options

- -40-pin Ceramic DIP (Suffix: -C)

-40-pin Plastic DIP (Suffix: -P)

## PIN ASSIGNMENT

PACKAGE DIP-40C-AD1

\*: No Connection

\* MB8876A: Negative Logic

MB8877A: Positive Logic

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance

circuit.

FUJITSU reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of FUJITSU LTD. or others.

## PIN DESCRIPTIONS

| Pin No. | Symbol          | Pin Name       | VO | Description                                                      |

|---------|-----------------|----------------|----|------------------------------------------------------------------|

| 20      | V <sub>SS</sub> | Danier Curalis |    | Ground (GND)                                                     |

| 21      | Vcc             | Power Supply   | '  | +5V DC supply                                                    |

| 24      | CLK             | Clock          | 1  | 2-MHz fixed frequency clock signal (1-MHz for mini-floppy disk). |

| 19      | MR              | Master Reset   | I  | Signal for resetting the FDC.                                    |

| 22      | TEST            | Test           | I  | Signal for setting the FDC into a test mode.                     |

| 1, 40   | NC              | Non Connection | -  | These pins are not used.                                         |

## MPU INTERFACE PINS

| 37     | DOEN                                                                       | Double Density       | 1   | Signal for selecting a FDC operation mode: When DDEN = 0, the double density operation mode is selected. When DDEN = 1, the single density operation mode is selected. This input must be fixed while the FDC is in busy state.                                                                              |

|--------|----------------------------------------------------------------------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3      | CS                                                                         | Chip Select          | ı   | Signal for controlling the DALs: When $\overline{CS}=0$ , the DALs are activated and data transfer between the FDC and the MPU is enabled. When $\overline{CS}=1$ , the DALs are in high impedance state and data transfer is inhibited. (i.e., $\overline{RE}$ and $\overline{WE}$ are ignored.)            |

| 4      | RE                                                                         | Read Enable          | 1   | Strobe signal provided when data is read from internal registers: When $\overrightarrow{CS} = \overrightarrow{RE} = 0$ , data can be read from internal registers.                                                                                                                                           |

| 2      | WE                                                                         | Write Enable         | ı   | Strobe signal provided when data is written into internal registers: When CS = WE = 0, data can be written internal registers.                                                                                                                                                                               |

| 5, 6   | A <sub>0</sub> , A <sub>1</sub>                                            | Register Select Line | -   | Signal for addressing an internal register among Command Register (CR), Status Register (STR), Track Register (TR), Sector Register (SCR) and Data Register (DR): Refer to table of REGISTER SELECTION (p. 6).                                                                                               |

| 7 ~ 14 | DAL <sub>0</sub> ~ DAL <sub>7</sub><br>DAL <sub>0</sub> ~ DAL <sub>7</sub> | Data Access Line     | 1/0 | 8-bit bidirectional bus for transferring 8-bit data between the FDC and the MPU. MB8876A: negative logic/MB8877A: positive logic.                                                                                                                                                                            |

| 38     | DRQ                                                                        | Data Request         | 0   | Signal for informing the MPU of a DR status: Read operation: DRQ = 1 shows the DR is filled with a 8-bit data from a disk, and the FDC is requesting for the MPU to read the data. Write operation: DRQ = 1 shows the DR is empty, and the FDC is requesting for the MPU to write the next data into the DR. |

| 39     | IRQ                                                                        | Interrupt Request    | 0   | Interrupt signal to the MPU: IRQ is set when a Command is completed or the TYPE IV Command is executed. IRQ is reset when the next Command is written or the STR is read.                                                                                                                                    |

## FLOPPY DISK INTERFACE PINS Disk Head Control Signal

| 15 | STEP | Step Move | O Step pulse signal for moving a disk head. |                                                                                                                                                              |

|----|------|-----------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | DIRC | Direction | 0                                           | Signal for indicating a direction of disk head moving to the FDD: DIRC = 0 shows the head moves toward outside. DIRC = 1 shows the head moves toward inside. |

| 28 | HLD  | Head Load | 0                                           | Signal for loading a disk head: When HLD = 1, the head is engaged on the disk. When HLD = 0, the head is released from the disk.                             |

## Disk Head Control Signal (Continued)

| Pin No. | Symbol | Pin Name         | I/O | Description                                                                                                                                                                                                                                                                                                                                          |

|---------|--------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | HLT    | Head Load Timing | I   | Signal for informing a disk head status: HLT = 1 shows a disk head is in an enagaged state. HLT is set when a disk head has been settled or a head settle time pre-determined by one shot circuit has elapsed after HLD = 1.                                                                                                                         |

| 34      | TR00   | Track 00         | -   | Signal for informing whether a disk head is positioned on Track No. 00 or not: TR00 = 0 shows Track No. 00 is detected during track seaking operation.                                                                                                                                                                                               |

| 32      | READY  | Ready            | ı   | Signal for informing the FDC of a disk drive status: READY = 1 shows the disk drive is ready for operation, and only when READY = 1, read/write operation for disk can be executed. READY = 0 shows the disk drive is not ready, and neither read/write operation cannot be executed. However, seek operation is executed regardless of this signal. |

| 35      | ΙĒ     | Index Pulse      | ı   | Signal for informing the FDC of an index hole of disk being detected in the FDD.                                                                                                                                                                                                                                                                     |

## **Disk Read Operation Signal**

| 25 | RG      | Read Gate  |   | Signal for informing synchronization between RCLK and RAWREAD to an external VFO circuit: RG = 1 show the FDC has found out a SYNC byte during disk reading operation. |

|----|---------|------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26 | RCLK    | Read Clock | 1 | A data window signal which is generated in an external VFO circuit out of Read Data.                                                                                   |

| 27 | RAWREAD | Raw Read   | ı | A raw read data signal transferred from the FDD.                                                                                                                       |

## **Disk Write Operation Signal**

| 30 | WG      | Write Gate                                               | 0   | Signal for indicating data is being written into a disk.                                                                                                                        |

|----|---------|----------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17 | EARLY   | Early Shift                                              | 0   | Signal for indicating early pre-compensation of data write timing to a disk: EARLY = 1 shows a serial data to be transmitted via the WD pin to a disk must be shifted earlier.  |

| 18 | LATE    | Late Shift                                               | 0   | Signal for indicating later pre-compensation of data write timing to a disk: LATE = 1 shows a serial data to be transmitted via the WD pin to a disk must be shifted later.     |

| 31 | WD      | Write Data                                               | 0   | A write data signal transferred to the FDD.                                                                                                                                     |

| 29 | TG43    | Track Greater<br>Than 43                                 | 0   | Signal for indicating a head position of a disk: TG43 = 1 shows the head is located on any Track No. 44 thru 76. TG43 = 0 shows the head is located on any Track No. 0 thru 43. |

| 33 | WF/VFOE | Write Fault/Variable<br>Frequency Oscil-<br>lator Enable | 1/0 | Input signal for informing a fault is detected during write operation for a disk (during WG $=$ 1). Output signal for informing the FDC is reading a disk (during WG $=$ 0).    |

| 34 | WPRT    | Write Protect                                            | 1   | Signal for inhibiting write operation for disk.                                                                                                                                 |

## REGISTER SELECTION

| Chip<br>Select | Address |                | Selecte               | Data Access Line Status |                                                                                                               |

|----------------|---------|----------------|-----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------|

| <u>cs</u>      | Α1      | A <sub>0</sub> | Read Mode (RE = 0)    | Write Mode (WE = 0)     | $\overline{\text{DAL}_7} \sim \overline{\text{DAL}_0}$ $\overline{\text{DAL}_7} \sim \overline{\text{DAL}_0}$ |

| 1              | *       | *              | Deselected            | Deselected              | High Impedance                                                                                                |

| 0              | 0       | 0              | Status Register (STR) | Command Register (CR)   | Enabled                                                                                                       |

| 0              | 0       | 1              | Track Register (TR)   | Track Register (TR)     | Enabled                                                                                                       |

| 0              | 1       | 0              | Sector Register (SCR) | Sector Register (SCR)   | Enabled                                                                                                       |

| 0              | 1       | 1              | Data Register (DR)    | Data Register (DR)      | Enabled                                                                                                       |

<sup>\*:</sup> Don't care

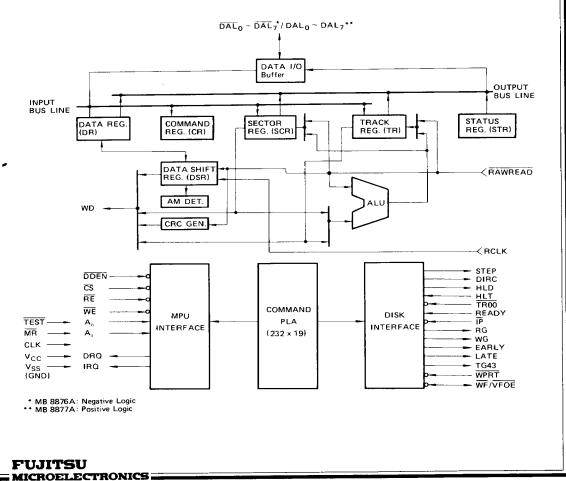

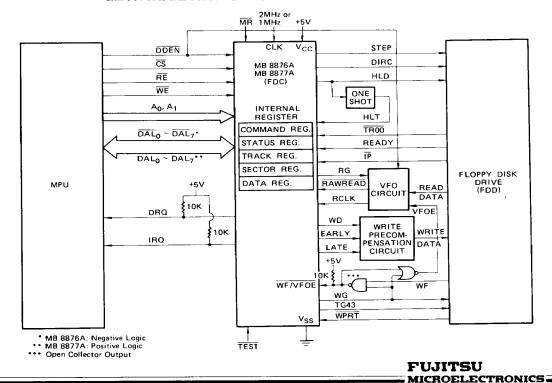

## MB8876A/MB8877A BLOCK DIAGRAM

<sup>4-30</sup>

#### FUNCTIONAL BLOCK DESCRIPTION

#### **INTERNAL REGISTERS**

#### Command Register (CR)

An 8-bit write-only register, holds the command which is being executed. This register should not be loaded when the BUSY flag is set (BUSY = 1) unless the execution of the current command is to be overridden, using the Force Interrupt command.

#### Status Register (STR)

An 8-bit read-only register, holds the device status information. The contents of STR are automatically updated according to the status of the executing Command. After the STR is read, the IRQ output is usually reset (IRQ = 0) except for the Type IV Command.

#### Data Register (DR)

An 8-bit read/write used as a holding register during Disk Read and Write operations. In Disk Read operations, the serial data assembled in the Data Shift Register is transferred to the DR, where it is made available to the data bus. In Disk Write operations, parallel data from the data bus is written into the DR where it is transferred to Data Shift Register. In a Seek Command, the data written into the DR holds the address of the desired Track address.

#### Data Shift Register (DSR)

An 8-bit shift register which cannot be accessed directly through the data bus. The DSR assembles serial data from the RAW READ input during Read operations and transfers the data to the DR. In Write operations, the DSR receives data from the DR and serially transfers it out through the WRITE DATA output.

#### • Track Register (TR)

An 8-bit read/write register, holds the track number of the current disk head position for Restore, Seek, Step, Step-In and Step-Out Commands (i.e. TYPE 1 Commands), and is updated during the Command execution. The TR contents are compared with the track number (recorded in the disk's ID field) during the contents are compared with the track number (recorded in the disk's ID field) during the contents are compared with the track number (recorded in the disk's ID field) during the contents are compared with the track number (recorded in the disk's ID field) during the contents are compared with the track number (recorded in the disk's ID field) during the contents are compared with the contents are c

ing Read, Write, and Verify operations. The TR should not be written to when the device is busy (BUSY = 1).

#### • Sector Register (SCR)

An 8-bit read/write register, holds the address of the desired sector number. The sector number is written into the SCR prior to the Read and Write Data Command execution. It should not be written to during busy (BUSY = 1). Executing the Read Address Command causes the SCR to be loaded with the track number from the ID field.

#### OTHER FUNCTIONAL BLOCKS

# Cycle Redundancy Check (CRC) Logic This logic is used for checking or generating the 16-bit Cycle Redundancy Check that is in the ID

and Data fields used for error detection. The polynominal is: G(X) = X16 + X12 + X5 + 1.

Arithmetic/Logic Unit (ALU)

The ALU is a serial comparator, incrementer, and decrementer used for register comparisons and modifications with the disk record ID fields.

#### • Address Mark (AM) Detection Circuit

A circuit to detect specific bit pattern data in the serial data from a disk (i.e. Index Mark, ID Address Mark, Data Address Mark).

#### Data Modulator

A circuit to modulate data to be written onto a disk in the specific recording format: Single density recording format: Frequency Modulation (FM) Double density recording format: Modified Frequency Modulation (MFM)

Programmable Logic Array (PLA) for Commands

A micro-program to generate control signals (Commands) which control the FDC operation: The size of micro-program is approximately 232 x 19 bits.

## BIT STRUCTURES OF COMMANDS

#### MB8876A/MB8877A

|      |                 |   |   |   | BIT | S  |    |                |    |

|------|-----------------|---|---|---|-----|----|----|----------------|----|

| TYPE | COMMAND         | 7 | 6 | 5 | 4   | 3  | 2  | 1              | 0  |

| ]    | Restore         | 0 | 0 | 0 | 0   | h  | V  | r1             | ro |

| 1    | Seek            | 0 | 0 | 0 | 1   | h  | V  | r1             | ro |

| I    | Step            | 0 | 0 | 1 | u   | h  | V  | r <sub>1</sub> | ro |

| I    | Step In         | 0 | 1 | 0 | u   | h  | V  | r <sub>1</sub> | ro |

| 1    | Step Out        | 0 | 1 | 1 | u   | h  | V  | r <sub>1</sub> | ro |

| 11   | Read Sector     | 1 | 0 | 0 | m   | S  | Ε  | С              | 0  |

| II   | Write Sector    | 1 | 0 | 1 | m   | S  | E  | С              | a0 |

| Ш    | Read Address    | 1 | 1 | 0 | 0   | 0  | Ε  | 0              | 0  |

| 111  | Read Track      | 1 | 1 | 1 | 0   | 0  | E  | 0              | 0  |

| III  | Write Track     | 1 | 1 | 1 | 1   | 0  | Ε  | 0              | 0  |

| IV   | Force Interrupt | 1 | 1 | 0 | 1   | lз | 12 | 11             | lo |

NOTE: Bits shown in TRUE form.

#### TABLE 1. STEPPING RATES

| CLK   | 2 MHz    | 2 MHz    | 1 MHz    | 1 MHz    | 2 MHz    | 1 MHz    |

|-------|----------|----------|----------|----------|----------|----------|

| DDEN  | 0        | 1        | 0        | 1        | x        | x        |

| R1 R0 | TEST = 1 | TEST = 1 | TEST = 1 | TEST = 1 | TEST = 0 | TEST = 0 |

| 0 0   | 3 ms     | 3 ms     | 6 ms     | 6 ms     | 184µs    | 368µs    |

| 0.1   | 6 ms     | 6 ms     | 12 ms    | 12 ms    | 190µs    | 380µs    |

| 1 0   | 10 ms    | 10 ms    | 20 ms    | 20 ms    | 198µs    | 396μs    |

| 1 1   | 15 ms    | 15 ms    | 30 ms    | 30 ms    | 208µs    | 416µs    |

#### TYPE I COMMANDS

#### h = Head Load Flag (Bit 3)

h = 1, Load head at beginning

h = 0, Unload head at beginning

#### V = Verify flag (Bit 2)

V = 1, Verify on destination track

V = 0, No verify

## $r_1r_0$ = Stepping motor rate (Bits 1-0)

Refer to Table 1 for rate summary

u = Update flag (Bit 4)

u = 1, Update Track register

u = 0, No update

#### TYPE II & III COMMANDS

#### m = Multiple Record flag (Bit 4)

m = 0, Single Record

m = 1, Multiple Records

## a<sub>0</sub> f = Data Address Mark (Bit 0)

a<sub>0</sub> = 0, FB (Data Mark)

a<sub>0</sub> = 1, F8 (Deleted Data Mark)

#### E = 15 ms Delay (2MHz)

E = 1, 15 ms delay

E = 0, no 15 ms delay

#### S = Side Select Flag

S = 0, Compare for Side 0

S = 1, Compare for Side 1

#### C = Side Compare Flag

C = 0, diable side select compare

C = 1, enable side select compare

## TYPE IV COMMAND

#### li = Interrupt Condition flags (Bits 3-0)

IO = 1, Not-Ready to Ready Transition

I1 = 1, Ready to No-Ready Transition

12 = 1, Index Pulse

I3 = 1, Immediate Interrupt

$I_3 - I_0 = 0$ , Terminate with no Interrupt

**FUJITSU**

MICROELECTRONICS \_\_

## STATUS REGISTER SUMMARY

| Command Status Bit |           |               |             |               |           |           | -     |      |

|--------------------|-----------|---------------|-------------|---------------|-----------|-----------|-------|------|

|                    | 7         | 6             | 5           | 4             | 3         | 2         | 1     | 0    |

| All Type I         | Not Ready | Write Protect | Head Loaded | Seek Error    | CRC Error | Track 0   | Index | Busy |

| Read Sector        | Not Ready | 0             | Record Type | Rec not Found | CRC Error | Lost Data | DRQ   | Busy |

| Write Sector       | Not Ready | Write Protect | Write Fault | Rec not Found | CRC Error | Lost Data | DRQ   | Busy |

| Read Address       | Not Ready | 0             | 0           | Rec not Found | CRC Error | Lost Data | DRQ   | Busy |

| Read Track         | Not Ready | 0             | 0           | 0             | 0         | Lost Data | DRQ   | Busy |

| Write Track        | Not Ready | Write Protect | Write Fault | 0             | 0         | Lost Data | DRQ   | Busy |

## STATUS DESCRIPTION FOR TYPE I COMMANDS

| Bit | Name        | Meaning                                                                                                                                                                            |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S7  | Not Ready   | This bit when set indicates the drive is not ready. When reset it indicates that the drive is ready. This bit is an inverted copy of the Ready input and logically 'ored' with MR. |

| S6  | Protected   | When set, indicates Write Protect is activated. This bit is an inverted copy of WRPT input.                                                                                        |

| S5  | Head Loaded | When set, it indicates the head is loaded and engaged. This bit is a logical "and" of HLD and HLT signals.                                                                         |

| S4  | Seek Error  | When set, the desired track was not verified. This bit is reset to 0 when updated.                                                                                                 |

| S3  | CRC Error   | CRC encountered in ID filed.                                                                                                                                                       |

| S2  | Track 00    | When set, indicates Read/Write head is positioned to Track 0. This bit is an inverted copy of the TR00 input.                                                                      |

| S1  | Index       | When set, indicates index mark detected from drive. This bit is an inverted copy of the IP input.                                                                                  |

| SO  | Busy        | When set command is in progress. When reset no command is in progress.                                                                                                             |

## STATUS DESCRIPTION FOR TYPE II AND III COMMANDS

| Bit | Name                        | Meaning                                                                                                                                                                                                                                            |

|-----|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S7  | Not Ready                   | This bit when set indicates the drive is not ready. When reset, it indicates that the drive is ready. This bit is an inverted copy of the Ready input and 'ored' with MR. The Type II and III Commands will not execute unless the drive is ready. |

| S6  | Write Protect               | On Read Record: Not Used. On Read Track: Not Used. On any Write: It indicates a Write Protect. This bit is reset when updated.                                                                                                                     |

| S5  | Record Type/<br>Write Fault | On Read Record: It indicates the record-type code from data field address mark. 1 = Deleted Data Mark. 0 = Data Mark. On any Write: It indicates a Write Fault. This bit is reset when updated.                                                    |

| S4  | Record Not<br>Found (RNF)   | When set, it indicates that the desired track, sector, or side were not found. This bit is reset when updated.                                                                                                                                     |

| S3  | CRC Error                   | If S4 is set, an error is found in one or more ID fields; otherwise it indicates error in data field. This bit is reset when updated.                                                                                                              |

| S2  | Lost Data                   | When set, it indicates the computer did not respond to DRQ in one byte time. This bit is reset to zero when updated.                                                                                                                               |

| S1  | Data Request                | This bit is a copy of the DRQ output. When set, it indicates the DR is full on a Read Operation or the DR is empty on a Write operation. This bit is reset to zero when updated.                                                                   |

| S0  | Busy                        | When set, command is under execution. When reset, no command is under execution.                                                                                                                                                                   |

4-34

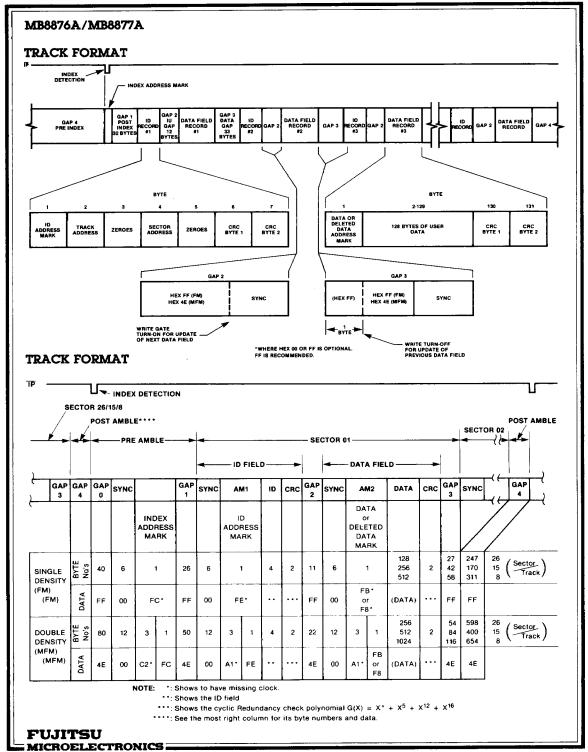

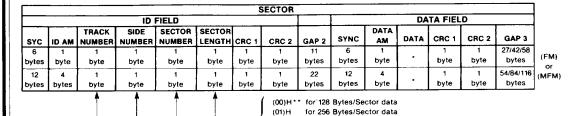

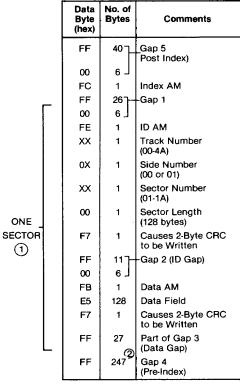

#### SECTOR FORMAT

(02)H

(03)H for 1024 Bytes/Sector data

(01)H to (1A)H for 26 Sector/Track format

(01)H to (0F)H for 15 Sector/Track format

(01)H to (08)H for 8 Sector/Track format

(00)H for Side 0 of single-side of double-side disk (01)H for Side 1 of double-side disk

412 Bytes/Sector data

(00)H to (4A)H for Track 0 thru Track 74\*\*\*

NOTE : Byte number of this column is defined in the SECTOR LENGTH column.

::: "H" after parentheses show that the parenthesized figures are hexa-decimal.

\*\*\*: Track 75 and 76 are usually used for correction.

## MB8876A/MB8877A TYPICAL SYSTEM CONSTRUCTION

4-35

#### IBM 3740 Format

This single-density (FM) format utilizes 128 bytes/ sector. The bytes to be generated by the system MPU for use in the execution of the Write Track command are shown below.

Notes: 1. This pattern must be written 26 times per track.

#### **IBM System 34 Format**

This double-density (MFM) format utilizes 256 bytes/ sector. The bytes to be generated by the system MPU for use in the execution of the Write Track command are shown below.

|        | Data<br>Byte<br>(hex) | No. of<br>Bytes | Comments                           |

|--------|-----------------------|-----------------|------------------------------------|

|        | 4E                    | 807             | _Gap 5<br>(Post Index)             |

|        | 00                    | 12_             |                                    |

|        | F6                    | 3               | Writes C2                          |

|        | FC                    | 1               | Index AM                           |

| _      | 4E                    | ן 50            |                                    |

|        | 00                    | 12 -            | -Gap 1                             |

|        | F5                    | 3               | Writes ID AM<br>Sync Bytes         |

|        | FE                    | 1               | ID AM                              |

|        | XX                    | 1               | Track Number<br>(00-4C)            |

|        | 0X                    | 1               | Side Number<br>(00 or 01)          |

|        | XX                    | 1               | Sector Number<br>(01-1A)           |

| ONE    | 01                    | 1               | Sector Length<br>(256 Bytes)       |

| SECTOR | F7                    | 1               | Causes 2-Byte CRC<br>to be Written |

| (1)    | 4E                    | 227             | Gap 2 (ID Gap)                     |

|        | 00                    | 12              |                                    |

|        | F5                    | 3               | Writes ID AM<br>Sync Bytes         |

|        | FB                    | 1               | Data AM                            |

|        | 40                    | 256             | Data Field                         |

|        | F7                    | 1               | Causes 2-Byte CRC<br>to be Written |

|        | 4E                    | 54              | Part of Gap 3<br>(Data Gap)        |

|        | 4E                    | 598             | Gap 4<br>(Pre Index)               |

Notes: 1. This pattern must be written 26 times per track.

2. Continue writing Hex 4E until FDC completes

Continue writing Hex 4E until FDC completes sequence and generates INTRQ interrupt.

**FUJITSU**

MICROELECTRONICS =

Continue writing Hex FF until FDC completes sequence and generates INTRQ interrupt.

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol                                               | Rating                                       | Unit |

|-----------------------|------------------------------------------------------|----------------------------------------------|------|

| Voltage on any pin    | V <sub>CC</sub> , V <sub>IN</sub> , V <sub>OUT</sub> | V <sub>SS</sub> -0.3 to V <sub>SS</sub> +7.0 | ٧    |

| Operating Temperature | TA                                                   | 0 to 70                                      | °C   |

| Storage Temperature   | T <sub>stg</sub>                                     | -55 to +150                                  | °C   |

Note: Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

|                    |                 |      | Value |      |      |                       |

|--------------------|-----------------|------|-------|------|------|-----------------------|

| Parameter          | Symbol          | Min  | Тур   | Max  | Unit | Operating Temperature |

| aValtago           | V <sub>CC</sub> | 4.75 | 5.00  | 5.25 | V    |                       |

| Supply Voltage     | V <sub>SS</sub> | _    | 0     | _    | •    | 0°C to +70°C          |

| Input High Voltage | V <sub>IH</sub> | 2.0  |       | Vcc  | V    | 0 0 10 +70 0          |

| Input Low Voltage  | V <sub>IL</sub> | -0.3 | _     | 0.8  | V    |                       |

## DC CHARACTERISTICS

(Recommended Operating Conditions unless otherwise noted.)

| Parameter                                                     | Symbol           | Min | Тур          | Max | Unit |

|---------------------------------------------------------------|------------------|-----|--------------|-----|------|

| Output High Voltage ( $I_{OH} = -200\mu A$ )                  | Voн              | 2.4 | _            | _   | V    |

| Output Low Voltage (I <sub>OL</sub> = 1.8mA)                  | VOL              |     |              | 0.4 | V    |

| Three-State (Off-State) Input Current (VIN = 0.4V to 2.4)     | ITSI             | _   | _            | 10  | μΑ   |

| Input Leakage Current (See Note 1)                            | l <sub>IN1</sub> | _   | _            | 2.5 | μΑ   |

| Input Leakage Current (See Note 2)                            | I <sub>IN2</sub> | _   |              | 100 | μΑ   |

| Output Leakage Current for Off-State (V <sub>OH</sub> = 2.4V) | ILOH             |     |              | 10  | μΑ   |

| Power Consumption                                             | PD               |     | <del>-</del> | 350 | mW   |

Note1) Except for HLT,  $\overline{\text{TEST}}$ ,  $\overline{\text{WF}}$ ,  $\overline{\text{WPRT}}$ , and  $\overline{\text{DDEN}}$ .  $(V_{\text{IN}}=0 \text{ to } 5.25 \text{V})$  2) For HLT,  $\overline{\text{TEST}}$ ,  $\overline{\text{WF}}$ ,  $\overline{\text{WPRT}}$ , and  $\overline{\text{DDEN}}$ .  $(V_{\text{IN}}=0 \text{ to } 5.25 \text{V})$

## **AC CHARACTERISTICS**

(Recommended Operating Conditions unless otherwise noted.)

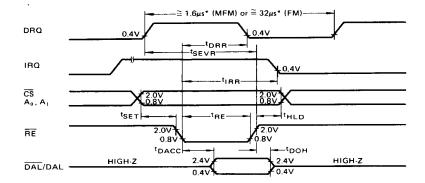

## MPU Read Timing (From FDC)

|                                         |                  |     | Value        |       |      |  |

|-----------------------------------------|------------------|-----|--------------|-------|------|--|

| Parameter                               | Symbol           | Min | Тур          | Max   | Unit |  |

| Address Setup Time                      | t <sub>SET</sub> | 50  |              |       | ns   |  |

| Address Hold Time                       | tHLD             | 10  |              |       | ns   |  |

| RE Pulse Width                          | t <sub>RE</sub>  | 280 | <del>-</del> |       | ns   |  |

| DRQ Reset Time                          | torr             |     |              | 250   | ns   |  |

| IRQ Reset Time                          | tirr             |     | _            | 500   | ns   |  |

| Data Delay Time (C <sub>L</sub> = 25pF) | †DACC            |     | <del>-</del> | 250   | ns   |  |

| Data Hold Time (C <sub>L</sub> = 25pF)  | <sup>†</sup> DOH | 50  | _            | 150   | ns   |  |

| DRQ Service Time (RCLK Cycle = 2μs)     | tsevr            |     |              | 13.5* | μs   |  |

<sup>\*:</sup> These values are doubled when CLK = 1MHz.

## **READ TIMING**

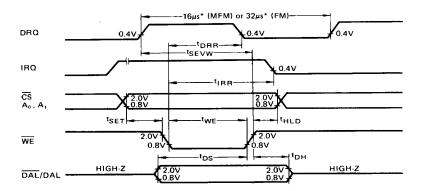

## MPU Write Timing (To FDC)

| Parameter                     | Symbol            | Min | Тур          | Max   | Unit |

|-------------------------------|-------------------|-----|--------------|-------|------|

| Address Setup Time            | tSET              | 50  | <del>_</del> | _     | ns   |

| Address Hold Time             | tHLD              | 10  | <del>-</del> |       | ns   |

| WE Pulse Width                | t <sub>WE</sub>   | 200 | <del></del>  |       | ns   |

| DRQ Reset Time                | t <sub>DRR</sub>  | _   |              | 250   | ns   |

| INTRQ Reset Time              | tire              | -   |              | 500   | ns   |

| Data Setup Time               | t <sub>DS</sub>   | 250 |              | =     | ns   |

| Data Hold Time                | t <sub>DH</sub>   | 0   | _            | _     | ns   |

| DRQ Service Time (DDEN = "L") | t <sub>SEVW</sub> |     | _            | 11.5* | μS   |

<sup>\*:</sup> These values are doubled when CLK = 1MHz.

## WRITE TIMING

<sup>\*:</sup> These values are doubled when CLK = 1MHz.

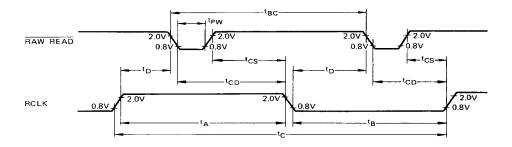

## FDC Read Data Timing (From Disk)

|                         |     |                 |     | Value        |      |      |

|-------------------------|-----|-----------------|-----|--------------|------|------|

| Parameter               |     | Symbol          | Min | Тур          | Max  | Unit |

| RAWREAD Pulse Width     |     | tpW             | 100 | _            | 250* | ns   |

| Clock Setup Time        |     | t <sub>D</sub>  | 40  | _            | _    | ns   |

| Clock Hold Time for MFM |     | t <sub>CD</sub> | 40  | _            | _    | ns   |

| Clock Hold Time for FM  |     | tcs             | 40  | _            | _    | ns   |

| DAMOFAD O Time          | MFM | t <sub>BC</sub> |     | 2*, 3* or 4* | _    | μS   |

| RAWREAD Cycle Time      | FM  |                 | _   | 2* or 4*     | _    | μS   |

| DOLK High Dules Width   | MFM |                 | 0.8 | 1*           | 20   | μS   |

| RCLK High Pulse Width   | FM  | t <sub>A</sub>  | 0.8 | 2*           | 20   | μS   |

| DOLK Law Bulan Midth    | MFM |                 | 0.8 | 1*           | 20   | μS   |

| RCLK Low Pulse Width    | FM  | t <sub>B</sub>  | 0.8 | 2*           | 20   | μS   |

|                         | MFM |                 |     | 2*           | _    | μS   |

| RCLK Cycle Time         | FM  | t <sub>C</sub>  | _   | 4*           |      | μS   |

<sup>\*:</sup> These values are double when CLK = 1MHz.

## READ DATA TIMING

## 4

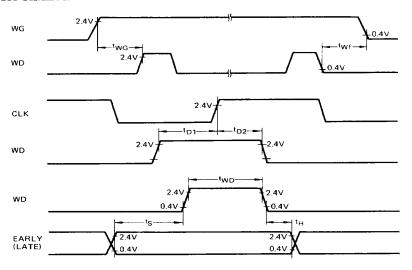

## FDC Write Data Timing (To Disk)

| D                            |                 |             |     |      | Value |       | Unit |

|------------------------------|-----------------|-------------|-----|------|-------|-------|------|

| Parameter                    | Symbol          | Condition   | Min | Тур  | Max   | Uiiit |      |

| Write Data Pulse Width       |                 | CLK = 2 MHz | FM  | 450  | 500   | 550   |      |

|                              | two**           |             | MFM | 150  | 200   | 250   | ns   |

| Write Gate To Write Data     |                 | CLK = 2 MHz | FM  | _    | 2     | _     | μS   |

|                              | twg**           |             | MFM |      | 1     | _     |      |

|                              | twr**           | CLK = 2 MHz | FM  | _    | 2     |       | μS   |

| Write Gate off from WD       |                 |             | MFM | 1    |       | 2     |      |

| Early (Late) to Write Data   | ts              | CLK = 2 MHz | MFM | 125  | -     | _     | ns   |

| Early (Late) from Write Data | t <sub>H</sub>  | CLK = 2 MHz | MFM | -50° | _     | _     | ns   |

|                              |                 | CLK = 1 MHz | MFM | 200  |       | _     |      |

| WD Valid to CLK              | t <sub>D1</sub> | CLK = 2 MHz | MFM | 30   | _     | _     | ns   |

|                              |                 | CLK = 1 MHz | MFM | 50   | _     | _     |      |

| WD Valid after CLK           | t <sub>D2</sub> | CLK = 2 MHz | MFM | 50   | _     | _     | ns   |

<sup>\*:</sup> This value, -50ns (min) indicated that Early (Late) signal changes 50ns (min) before WD falls down in worst case. See DISK DATA OUTPUT TIMING.

## WRITE DATA TIMING

<sup>\*\*:</sup> All times are doubled when CLK = 1 MHz.

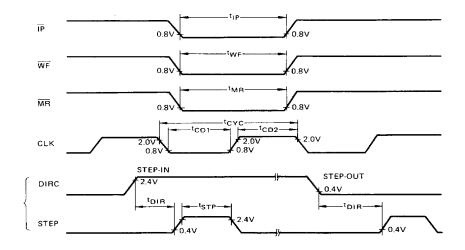

## OTHER TIMINGS

|                      |     |                  |     | Value |              |      |

|----------------------|-----|------------------|-----|-------|--------------|------|

| Parameter            |     | Symbol           |     | Тур   | Max          | Unit |

| CLK Low Pulse Width  |     | t <sub>CD1</sub> | 230 | _     | 20000        | ns   |

| CLK High Pulse Width |     | t <sub>CD2</sub> | 200 | _     | 20000        | ns   |

| STEP Pulse Width     | MFM | •                | 2*  |       | _            | μS   |

|                      | FM  | <sup>t</sup> STP | 4*  | _     | _            | μS   |

| DIRC Setup Time      | 1   | t <sub>DIR</sub> | 12* | _     | <del>-</del> | μS   |

| MR Pulse Width**     |     | t <sub>MR</sub>  | 50* | _     | <u> </u>     | μS   |

| IP Pulse Width       |     | t <sub>IP</sub>  | 10* | _     | <u> </u>     | μS   |

| WF Pulse Width       |     | t <sub>WF</sub>  | 10* | _     | -            | μS   |

| CLK Cycle Time       |     | tcyc             | _   | 0.5*  | _            | μS   |

<sup>\*:</sup> These Values are doubled when CLK = 1MHz.

## OTHER TIMINGS

FUJITSU

<sup>\*\*:</sup> During Master Reset, CLK of more than 10 cycles are required.

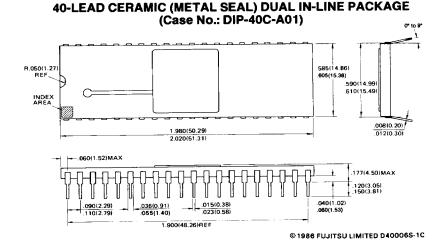

## PACKAGE DIMENSIONS Dimensions in inches (millimeters)

# 40-LEAD PLASTIC DUAL IN-LINE PACKAGE (Case No.: DIP-40P-M01)